# DEVISE OF NULL CONGREGATION LOGIC CIRCUIT WITH OUT RESISTER

# Mr.K.RAGHU<sup>1</sup>, Mr.P.NAGARAJU<sup>2</sup>

<sup>1</sup>Assistant Professor, International School of Technology and Sciences for Women, Rajanagaram, Andhra Pradesh-533294.

<sup>2</sup>Associate Professor, International School of Technology and Sciences for Women, Rajanagaram, Andhra Pradesh-533294.

## **ABSTRACT:**

Self-timed properly judgment layout strategies are advanced the usage of Threshold Combinational Reduction (TCR) in the NULL Convention Logic (NCL) paradigm. NCL correct judgment abilties are found out using 27 incredible transistor networks imposing the set of all capabilities of four or fewer variables, therefore facilitating a variety of gate degree optimizations. TCR optimizations are formalized for NCL after which assessed by manner of comparing levels of gate delays, gate counts, transistor counts, and strength utilization of the ensuing designs. The conventional shape of Boolean good judgment isn't symbolically entire in the revel in that it requires the participation of a basically special shape of expression, time in the form of the clock, which has to be very cautiously coordinated with the logic part of the expression to certainly and effectively specific away. With the lower of transistor feature sizes into the extremely-deep submicron variety, leakage energy will become a crucial design task for circuit designers. This paper examines the application of an asynchronous layout paradigm named Multi-Threshold NULL Convention Logic to adaptive beam forming circuits. Overall, the twin-rail designs are each quicker and require an awful lot less area than their respective quad-rail opposite numbers; but, the quadrail variations are predicted to devour much less electricity.

Keywords: -Carry-save addition, low-cost architecture, Montgomery modular multiplier, public-key cryptosystem.

### 1. INTRODUCTION:

of Presently, the development synchronous circuits dominates the semiconductor organisation. However, there are essential restricting factors to this layout method, together with clock distribution, growing clock rates. characteristic reducing size, immoderate power consumption, and timing closure try. Correct-throughasynchronous production circuits, such as NCL, were established to require plenty much less electricity, generate much less noise, produce less EMI, and allow for simpler reuse of components, in comparison to their synchronous contrary numbers, with compromising overall out performance. Additionally, leakage strength has come to dominate power intake as device sizes lessen. Adaptive beam forming circuits have many packages wherein decrease power is quite desirable without sacrificing

standard overall performance. These structures regularly require GHz range of throughput to residence the fast input facts circulate, on the equal time as having long idle periods between devices of sports activities. In order to lessen power, asynchronous layout methods have come to be increasingly attractive over the last decades. Quasioff-insensitive (QDI) cast asynchronous circuits, which includes NULL Convention Logic (NCL) do now not use a clock; instead, they include handshaking protocols to govern the circuit's conduct. Also, the self-timed nature of accurate-by using-introduction SoCs should allow for formerly designed and showed practical blocks to be reused in next designs, without necessitating any large adjustments or retiming attempt interior a reused useful block, and may offer for less complicated interfacing among the digital core and non-conventional purposeful blocks.

Therefore one of the first duties that need to be undertaken so that it will assisting combine NCL into the semiconductor format organization is design and symbolize to key components, that allows you to shape a library of reusable designs. Of fundamental significance are arithmetic circuits, together with the ALUs, evolved and in contrast in this paper. An evaluation of the NULL Convention Logic (NCL) paradigm is provided in the next section.

#### 2. PREVIOUS STUDY:

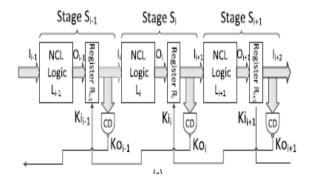

traditional NCL Both the and MTNCL paradigms require pipeline registers for keeping apart neighboring common sense modules, to be able to prevent a DATA/NULL token from overriding its preceding NULL/DATA token due to latency distinction among pipeline ranges. However, pipeline registers account for as much as 35% of usual of electricity dissipation the NCL/MTNCL circuit. This quick

gives the Register-Less NCL (RL-NCL) design paradigm, which achieves low strength intake by both doing away with the pipeline registers and helping pleasant-grained strength gating. NCL gives a self-timed logic paradigm where manipulate inherent with each datum. NCL follows the so-called "weak situations" of Seitz's postponeinsensitive signaling scheme. As with self-timed logic techniques other mentioned herein, the NCL paradigm assumes that forks in wires are isochoric. MTNCL gets rid of the two unique layout requirements of NCL, i.e., input-completeness and observability. Also, MTNCL gates do now not want hysteresis, which is required for NCL gates, due to the fact the NULL wave front generated at once through the sleep signal. Consequently, in spite of the introduction of two sleep transistors, MTNCL circuits are smaller in area than equivalent NCL circuits. This paper specializes in the blessings of MTNCL in the postpone gadgets of an adaptive beam former, particularly the FTD and CTD. The remainder of this paper can be divided into three principal sections. The Approach phase will give an outline of the layout of the FTD and CTD. The Results section will provide a contrast between MTNCL and synchronous variations of the FTD and CTD. The Conclusion segment will offer very last thoughts as well as opportunities for destiny studies.

#### 3. PROPOSED METHODOLOGY:

The FTD unit itself is in fact a finite impulse reaction (FIR) filter out. FIR filters are broadly used in sign processing applications because of their stability and linear segment residences. The FTD unit uses three essential additives so as to perform the discrete convolution: shift registers to create facts faucets, Dadda multipliers to multiply the constant coefficients with the information, and carry choose adders to calculate the

final output. All numbers are in a hard and fast-factor fractional 2's complement layout; consequently, no overflow can occur at some stage in multiplication. All bits of precision are saved till the very last stage wherein the output is truncated to 12 bits of precision. Figure shows the FTD structure. . One type of threshold gate is the THmn gate, where 1pmpn; as depicted in Fig. A THmn gate corresponds to an operator with as a minimum m alerts asserted as its set situation and all indicators de-asserted as its reset circumstance. THmn gates have n inputs. At least m of the n inputs must be asserted before the output will become asserted. Because threshold gates are designed with hysteresis, all asserted inputs need to be de-asserted earlier than the output can be de-asserted. Hysteresis is used to offer a method for monotonic transitions and a whole transition of multi-rail inputs returned to a NULL state earlier than putting forward the output associated with the subsequent

wavefront of input statistics. In the symbol for a THmn gate, every of the n inputs is connected to the rounded part of the gate; the output emanates from the pointed end of the gate; and the gate's threshold cost, m; is written inner of the gate. An orphan is described as a cord that transitions during the modern-day DATA wavefront however isn't always used in the willpower of the output. Orphans are as a result of wire forks and can be overlooked via the isochoric fork assumption, so long as they are no longer allowed to cross a gate boundary. This observability situation, also known as indictability or stability, ensures that every gate transition is observable on the output; because of this that each gate those transitions is important to transition at least one of the outputs. When a DATA wave front passes into the register, the crowning glory detection issue outputs a request-for-NULL to the preceding degree in the pipeline. As shown in Figure, there is no

additional circuitry required for sleep era due to the fact sign handshaking indicators may be used immediately to sleep statistics while a NULL wave front is obtained. In this way, every combinational logic block alternates between DATA and NULL fronts. The MTNCL shift checks in is made from alternating registers which might be resettable to NULL and resettable to DATA, respectively. Typically, MTNCL registers (one DATA resettable and NULL-resettable) would enough for every tap in a shift register; but. to maximise the throughput, an additional MTNCL registers were delivered to each tap. Without this optimization, the shift sign up ought to look ahead to all different records to complete calculating earlier than shifting in new records. thereby decreasing the throughput. Adding these registers balances the pipeline degrees in the multipliers and adders with the range of tiers within the shift sign in. This

lets in the DATA wave front within the FTD to propagate rapidly after new information is acquired.

Fig.3.1. N-bit completion component.

#### 4. SIMULATION RESULTS:

Hysteresis ensures a complete transition of inputs again to NULL earlier than maintaining the output associated with the subsequent wave front of enters statistics. Therefore, a THnn gate is equivalent to an n-enter C-detail and a TH1n gate is equivalent to an n-input OR gate. In a THmn gate, every of the n inputs are hooked up to the rounded portion of the gate; the output emanates from the pointed cease of the gate; and the gate's threshold fee, m, is written inside of the gate. NCL threshold gates might

also consist of a reset input to initialize the output. Resettable gates are denoted via either a D or an N inside appearing the gate, in conjunction with the gate's threshold, regarding the gate being reset to common sense 1 or logic respectively. The CTD is made up of primarily registers, so this layout isn't always capable of take complete gain MTNCL. of the advantages of However, the CTD is drastically smaller than the FTD and consumes less than 10% strength when as compared with the FTD. Therefore, with FTD and CTD combined as a beam former channel, the electricity benefit of MTNCL nonetheless holds (three.7% universal saving in lively power and 36% saving in leakage electricity). However, when the input statistics fee is high (e.g., 700 MHz), MTNCL implementation the the advantage reveals of lower electricity due to the fact logic blocks in MTNCL have a lower chance of being sound asleep underneath

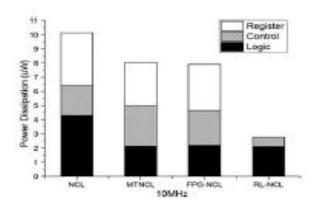

excessive input information price. In contrast, in Table I and Fig, it's miles shown that the proposed RL-NCL always achieves decrease electricity consumption than the conventional NCL both at low and excessive input charges. The benefit of low electricity inside the **RL-NCL** dissipation paradigm comes from the following: 1) eliminating pipeline registers; 2) changing complicated of completion detectors with less complicated OR gates; and three) mitigating leakage power of slumbering logic blocks through high-quality-grained The RLNCL gating. power implementation of the Kogge-Stone adder can reduce power dissipation by means of seventy two.5% and sixty two.5%, respectively, for the enter information costs of 10 and sevenhundred MHz, compared with the traditional NCL counterpart.

Fig.4.2. Power dissipation comparison of four NCL.

#### 5. CONCLUSION:

The MTNCL designs have been accomplished and simulated within the IBM 45nm PDSOI method to discover the maximum throughput that could be executed. For the FTD, the common throughput become 1.22 GHz, while the CTD had a mean throughput of one.89 GHz which might meet the standards for GHz variety throughput required through excessive-typical performance beam forming circuits. However. the application of embedded registration to the non-pipelined format, found via applying NCR yielded a giant more increase in throughput over the

authentic non-pipelined design, as opposed to the throughput boom accomplished through pipelining the layout for every twin-rail and quadrail architectures. Furthermore, this NCR method required fewer regions than pipelining for the dual-rail structure and simplest slightly more vicinity than pipelining for the quadrail structure.

#### **REFERENCES:**

- [1]. K. M. Fant and S. A. Brandt, "NULL Convention Logic: A Complete and Consistent Logic for Asynchronous Digital Circuit Synthesis," Intl. Conf. on Application Specific Systems, Architectures, and Processors, pp. 261-273, 1996.

- [2]. S. C. Smith and J. Di, "Designing asynchronous circuits using NULL convention logic (NCL)," Synth. Lect. Digit. Circuits Syst., vol. 4, no. 1, pp. 1–96, 2009.

- [3]. R. Mehboob, S. A. Khan, and R. Qamar, "FIR filter design methodology for hardware optimized implementation," IEEE Transactions

- on Consumer Electronics, vol.55, no.3, pp.1669-1673, August 2009.

- [4]. V. M. Dhivya, A. Sridevi, A. Ahilan, "A high speed area efficient FIR filter using floating point dadda algorithm," 2014 International Conference on Communications and Signal Processing (ICCSP), pp.1640-1644, April 2014.

- [5] K. M. Fant and S. A. Brandt, "NULL Convention Logic: A Complete and Consistent Logic for Asynchronous Digital Circuit Synthesis," International Conference on Application Specific Systems, Architectures, and Processors, pp. 261-273, 1996.

- [6] T. Verhoff, "Delay-Insensitive Codes An Overview," Distributed Computing, Vol. 3, pp. 1-8, 1988.

- [7] G. E. Sobelman and K. M. Fant, "CMOS Circuit Design of Threshold Gates with Hysteresis," IEEE International Symposium on Circuits and Systems (II), pp. 61-65, 1998.

- [8] A. Kondratyev, L. Neukom, O. Roig, A. Taubin, and K. Fant,

"Checking delay-insensitivity: 104 gates and beyond," Eighth International Symposium on Asynchronous Circuits and Systems, pp. 137-145, 2002.

[9] S. C. Smith, Gate and Throughput Optimizations for NULL Convention Self-Timed Digital Circuits, Ph.D. Dissertation, School of Electrical Engineering and Computer Science, University of Central Florida, 2001.